Difference between revisions of "Aufgaben:Exercise 1.6: Cyclic Redundancy Check"

| Line 5: | Line 5: | ||

}} | }} | ||

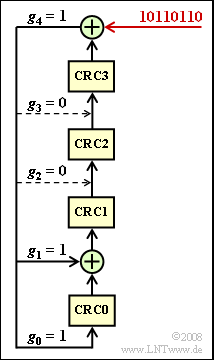

| − | [[File:|right|frame|]] | + | [[File:P_ID1626__Bei_A_1_6.png|right|frame|Bildung der CRC4-Prüfsumme]] |

Die Synchronisation geschieht beim Primärmultiplexanschluss jeweils im Kanal $0$ – dem Synchronisationskanal – eines jeden Rahmens. Bei ungeraden Zeitrahmen (Nummer 1, 3, ... , 15) überträgt dieser das sog. Rahmenkennwort mit dem festen Bitmuster '''X001 1011''', während jeder gerade Rahmen (mit Nummer 2, 4, ... , 16) das ''Meldewort'' '''X1DN YYYY''' beinhaltet. Über das D–Bit und das N–Bit werden Fehlermeldungen signalisiert. Die vier Y–Bits sind für Service–Funktionen reserviert. | Die Synchronisation geschieht beim Primärmultiplexanschluss jeweils im Kanal $0$ – dem Synchronisationskanal – eines jeden Rahmens. Bei ungeraden Zeitrahmen (Nummer 1, 3, ... , 15) überträgt dieser das sog. Rahmenkennwort mit dem festen Bitmuster '''X001 1011''', während jeder gerade Rahmen (mit Nummer 2, 4, ... , 16) das ''Meldewort'' '''X1DN YYYY''' beinhaltet. Über das D–Bit und das N–Bit werden Fehlermeldungen signalisiert. Die vier Y–Bits sind für Service–Funktionen reserviert. | ||

Revision as of 19:04, 29 November 2017

Die Synchronisation geschieht beim Primärmultiplexanschluss jeweils im Kanal $0$ – dem Synchronisationskanal – eines jeden Rahmens. Bei ungeraden Zeitrahmen (Nummer 1, 3, ... , 15) überträgt dieser das sog. Rahmenkennwort mit dem festen Bitmuster X001 1011, während jeder gerade Rahmen (mit Nummer 2, 4, ... , 16) das Meldewort X1DN YYYY beinhaltet. Über das D–Bit und das N–Bit werden Fehlermeldungen signalisiert. Die vier Y–Bits sind für Service–Funktionen reserviert.

Das X–Bit wird jeweils durch das CRC4–Verfahren gewonnen, dessen Realisierung in der Grafik dargestellt ist. Aus jeweils acht Eingangsbits – in der gesamten Aufgabe wird hierfür die Bitfolge 1011 0110 angenommen – werden durch Modulo–2–Additionen und Verschiebungen die vier Prüfbits CRC3, ... , CRC0 gewonnen, die dem Eingangswort in dieser Reihenfolge hinzugefügt werden.

Bevor das erste Bit in das Register geschoben wird, sind alle Register mit Nullen belegt:

- $${\rm CRC3 = CRC2 =CRC1 =CRC0 = 0}\hspace{0.05cm}.$$

Nach $8$ Schiebetakten steht in den vier Registern CRC3, ... , CRC0 die CRC4–Prüfsumme.

Die Anzapfungen des Schieberegisters sind $g_{0} = 1, g_{1} = 1, g_{2} = 0, g_{3} = 0$ und $g_{4} = 1$. Das dazugehörige Generatorpolynom lautet:

- $$G(D) = D^4 + D +1 \hspace{0.05cm}.$$

Die sendeseitige CRC4–Prüfsumme erhält man auch als Rest der Polynomdivision

- $$(D^{11} +D^{9} +D^{8}+D^{6}+D^{5})/G(D) \hspace{0.05cm}.$$

Das Divisorpolynom ergibt sich aus der Eingangsfolge und vier angehängten Nullen: 1011 0110 0000. Auch die CRC4–Überprüfung beim Empfänger (siehe Teilaufgabe 4) kann durch eine Polynomdivision dargestellt werden. Sie lässt sich durch eine Schieberegisterstruktur in ähnlicher Weise realisieren wie die sendeseitige Gewinnung der CRC4–Prüfsumme.

Hinweis:

Die Aufgabe gehört zum Themengebiet von ISDN–Primärmultiplexanschluss des vorliegenden Buches. Zur Lösung der Aufgabe werden einige Grundkenntnisse der Kanalcodierung vorausgesetzt.

Fragebogen

Musterlösung

(1) (2) (3) (4) (5) (6) (7)