Difference between revisions of "Exercise 2.5: DSL Error Protection"

From LNTwww

| Line 5: | Line 5: | ||

}} | }} | ||

| − | [[File: | + | [[File:EN_Bei_A_2_5.png|right|frame|$\rm ADSL$ error protection]] |

Latest revision as of 19:32, 25 March 2023

In order to decisively reduce the bit error rate of $\rm xDSL$ systems, various backup procedures have been proposed in the specifications to counteract the two most common causes of errors:

- Bit errors due to impulse and crosstalk interference on the (two-wire) line,

- clipping of signal peaks due to lack of dynamic range of the transmit amplifiers (clipping).

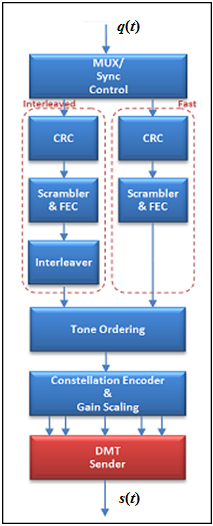

The diagram shows the error protection measures for $\rm ADSL/DMT$. These are implemented in two different paths:

- In the fast-path one relies on lower waiting times.

- In the interleaved-Path a lower bit error rate is expected.

The assignment of the bits to these paths is done by a multiplexer $\rm (MUX)$ with synchronization control.

Hint:

- This exercise belongs to the chapter "Methods to Reduce the Bit Error Rate in DSL".

Questions

Solution

(1) Correct are statements 1 and 3:

- Due to the lack of an interleaver in the fast-path, this path is less protected against bunching errors.

- On the other hand, for AWGN noise, an interleaver does not reduce the bit error rate.

- The disadvantage of an interleaver is the large waiting times (latency), since this distributes the input bits over a large time range in order to turn bundle errors into single errors after the de-interleaver, which is constructed in the same way, and which can then be removed by forward error correction (FEC).

(2) Correct statements 1, 3, and 4:

- Both the "CRC" (Cyclic Redundancy Check) as well as "Scrambler/De-scrambler" are implemented with shift registers of length $8$ and $23$ respectively.

- The scrambler is redundancy-free (that is, it has exactly as many output bits as input bits) and is self-synchronizing after a short run-in time.

- The redundancy of CRC is very low. It is not error correction in the true sense, but rather control of particularly important data, such as that for frame synchronization.

(3) Correct statements 2 and 3:

- In the $\rm LNTww$–book "Channel Coding", there is a detailed chapter on the" Reed-Solomon Codes".

- These are byte-level block codes, i.e., not symbol-by-symbol coding.

(4) Correct are statements 1 and 2 in contrast to the last two:

- The "Interleaving" is redundancy-free and results in large latency and delay, so it should be avoided for real-time applications.

(5) All of the above statements are correct, as can be read in detail on the "Gain scaling and tone ordering" page.